專用集成電路CMOS組合邏輯設(shè)計 集成電路設(shè)計的核心基石

在當(dāng)今信息技術(shù)的浪潮中,專用集成電路(ASIC)扮演著至關(guān)重要的角色,它為實(shí)現(xiàn)特定功能提供了高效、定制化的硬件解決方案。而在ASIC設(shè)計的廣闊領(lǐng)域中,基于CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)工藝的組合邏輯設(shè)計,構(gòu)成了其最基礎(chǔ)、最核心的數(shù)字電路設(shè)計模塊。本文旨在探討專用集成電路中CMOS組合邏輯設(shè)計的關(guān)鍵概念、設(shè)計流程及其在現(xiàn)代集成電路設(shè)計中的重要性。

CMOS技術(shù)與組合邏輯

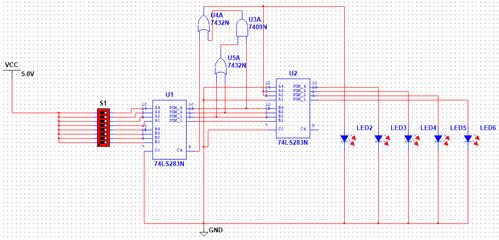

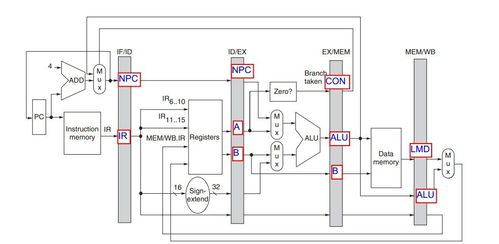

CMOS技術(shù)因其極低的靜態(tài)功耗、高噪聲容限以及與納米級制造工藝的良好兼容性,已成為現(xiàn)代數(shù)字集成電路的絕對主流。組合邏輯電路,顧名思義,其輸出僅取決于當(dāng)前的輸入信號組合,不包含任何存儲元件(如觸發(fā)器),因此不具有記憶功能。常見的組合邏輯電路包括與門、或門、非門、與非門、或非門、異或門、多路復(fù)用器、譯碼器和編碼器等。這些基本門電路是構(gòu)建更復(fù)雜數(shù)字系統(tǒng)(如算術(shù)邏輯單元、控制單元)的“磚石”。

CMOS組合邏輯設(shè)計的基本原理

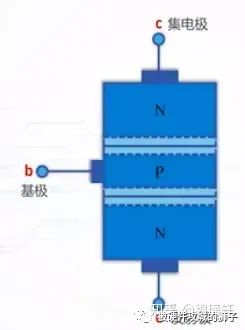

CMOS組合邏輯門的設(shè)計,本質(zhì)上是利用PMOS晶體管和NMOS晶體管的互補(bǔ)特性來構(gòu)建邏輯功能。基本設(shè)計原則可概括為:

1. 下拉網(wǎng)絡(luò)(PDN):由NMOS晶體管構(gòu)成,負(fù)責(zé)實(shí)現(xiàn)邏輯函數(shù)的“真”值部分(即輸出為邏輯0的條件)。當(dāng)輸入滿足特定組合時,PDN導(dǎo)通,將輸出節(jié)點(diǎn)拉低至地電平(邏輯0)。

2. 上拉網(wǎng)絡(luò)(PUN):由PMOS晶體管構(gòu)成,負(fù)責(zé)實(shí)現(xiàn)邏輯函數(shù)的“假”值部分(即輸出為邏輯1的條件)。當(dāng)輸入不滿足PDN導(dǎo)通條件時,PUN導(dǎo)通,將輸出節(jié)點(diǎn)拉高至電源電壓(邏輯1)。

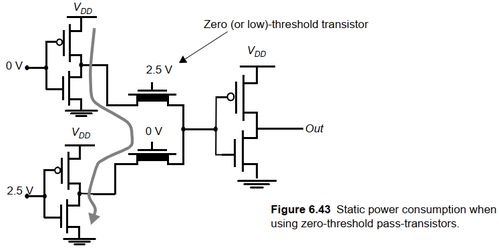

PUN和PDN在電氣特性上互為對偶,確保在任何靜態(tài)輸入組合下,兩條通路不會同時導(dǎo)通,從而實(shí)現(xiàn)了極低的靜態(tài)功耗。

設(shè)計流程與考量因素

一個穩(wěn)健的CMOS組合邏輯設(shè)計流程通常包括以下步驟:

- 邏輯功能定義與優(yōu)化:首先使用硬件描述語言(如Verilog或VHDL)或邏輯圖明確定義所需功能,并利用卡諾圖或邏輯綜合工具進(jìn)行布爾邏輯優(yōu)化,以最小化門級復(fù)雜度。

- 電路結(jié)構(gòu)選擇:根據(jù)性能、面積和功耗要求,選擇合適的電路結(jié)構(gòu)。例如,靜態(tài)CMOS邏輯是最可靠、最常用的結(jié)構(gòu);而動態(tài)CMOS邏輯、傳輸門邏輯等則在特定場景(如高性能、高密度)下有其優(yōu)勢。

- 晶體管尺寸確定(尺寸標(biāo)注):這是設(shè)計的關(guān)鍵環(huán)節(jié)。需要根據(jù)驅(qū)動能力、負(fù)載電容、上升/下降時間(時序要求)和功耗約束,精心計算每個晶體管的寬長比(W/L)。通常使用模擬電路仿真工具(如SPICE)進(jìn)行反復(fù)迭代驗證。

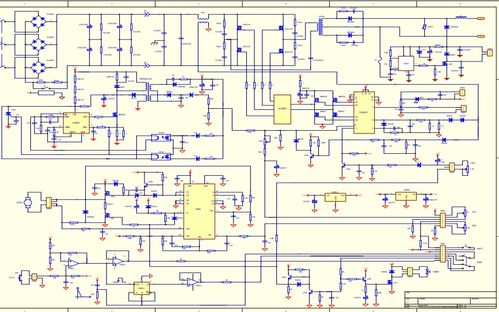

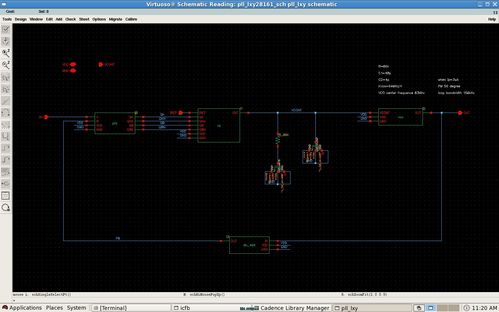

- 版圖設(shè)計與驗證:將電路圖轉(zhuǎn)換為符合特定CMOS工藝設(shè)計規(guī)則的物理掩膜版圖。這需要考慮晶體管布局、布線、寄生參數(shù)(電阻、電容)、信號完整性、電源網(wǎng)絡(luò)和可靠性(如天線效應(yīng)、閂鎖效應(yīng))等諸多因素。版圖后提取參數(shù)并再次進(jìn)行仿真驗證至關(guān)重要。

- 時序與功耗分析:在設(shè)計的各個階段,都需要對電路的傳播延遲、建立/保持時間以及動態(tài)/靜態(tài)功耗進(jìn)行嚴(yán)格分析和優(yōu)化,以滿足系統(tǒng)級指標(biāo)。

面臨的挑戰(zhàn)與未來趨勢

隨著工藝節(jié)點(diǎn)不斷向7納米、5納米甚至更小尺寸演進(jìn),CMOS組合邏輯設(shè)計面臨著前所未有的挑戰(zhàn):

- 短溝道效應(yīng)與泄漏電流:晶體管尺寸縮小導(dǎo)致亞閾值泄漏電流急劇增加,靜態(tài)功耗管理變得異常困難。

- 工藝波動與可靠性:制造過程中的微小變異對電路性能的影響愈發(fā)顯著,設(shè)計必須考慮工藝角(Process Corner)和蒙特卡洛分析以確保良率。

- 互連線延遲主導(dǎo):在深亞微米工藝下,互連線(金屬線)的電阻和電容導(dǎo)致的延遲已超過晶體管本身,成為時序性能的主要瓶頸。

為應(yīng)對這些挑戰(zhàn),設(shè)計方法學(xué)也在不斷發(fā)展,例如廣泛采用標(biāo)準(zhǔn)單元庫、基于時序驅(qū)動的綜合與布局布線流程、以及引入多閾值電壓(Multi-Vt)、電源門控(Power Gating)、近閾值計算(Near-Threshold Computing)等低功耗設(shè)計技術(shù)。

###

總而言之,CMOS組合邏輯設(shè)計是專用集成電路設(shè)計的基石。它不僅僅是簡單門電路的堆砌,更是一門在性能、功耗、面積和可靠性之間尋求精妙平衡的藝術(shù)與科學(xué)。深入理解其基本原理,熟練掌握從邏輯到版圖的全流程設(shè)計方法與EDA工具,是每一位集成電路設(shè)計工程師必備的核心技能。隨著芯片復(fù)雜度指數(shù)級增長和“摩爾定律”的演進(jìn),CMOS組合邏輯設(shè)計將繼續(xù)作為創(chuàng)新與突破的起點(diǎn),推動著從人工智能加速器到物聯(lián)網(wǎng)終端等各類專用芯片的飛速發(fā)展。

如若轉(zhuǎn)載,請注明出處:http://www.braccialini.com.cn/product/60.html

更新時間:2026-04-14 14:39:45