從零開始 利用立創(chuàng)商城資源實現(xiàn)單片機集成電路設(shè)計全流程指南

在當(dāng)今硬件創(chuàng)新蓬勃發(fā)展的時代,單片機(MCU)作為智能設(shè)備的核心,其集成電路(IC)設(shè)計已不再是大型半導(dǎo)體公司的專屬領(lǐng)域。得益于成熟的供應(yīng)鏈平臺與開源工具,獨立開發(fā)者與小型團隊也能涉足這一領(lǐng)域。立創(chuàng)商城,作為國內(nèi)領(lǐng)先的電子元器件與PCB服務(wù)一站式平臺,為這一旅程提供了關(guān)鍵的資源與跳板。本文旨在為你勾勒一條清晰、可行的路徑,指導(dǎo)你如何從零開始,借助立創(chuàng)商城等資源,完成一個簡易單片機系統(tǒng)的集成電路設(shè)計與實現(xiàn)。

第一階段:知識儲備與需求定義(“從零”的起點)

在動手之前,堅實的基礎(chǔ)至關(guān)重要。

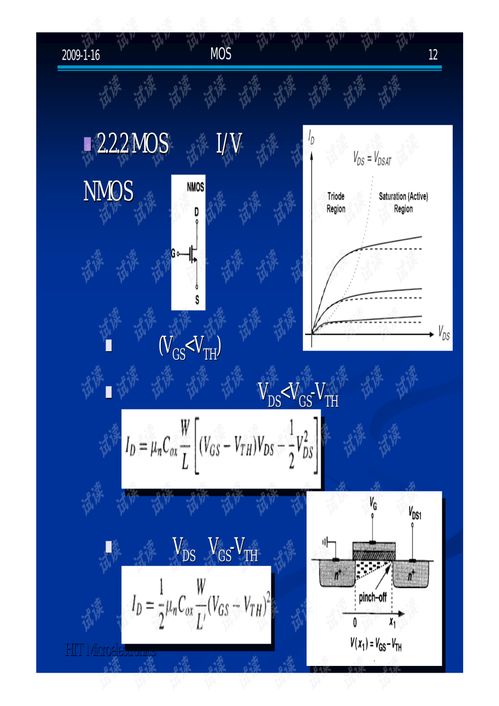

- 核心知識學(xué)習(xí):你需要掌握數(shù)字電路與模擬電路基礎(chǔ)、硬件描述語言(如Verilog或VHDL)、計算機體系結(jié)構(gòu)(了解CPU、總線、存儲器工作原理)以及單片機架構(gòu)知識。熟悉一種EDA(電子設(shè)計自動化)工具是必須的,例如開源的KiCad、EasyEDA(立創(chuàng)EDA),或商業(yè)軟件如Altium Designer。

- 明確設(shè)計目標(biāo):你的“單片機”具體要實現(xiàn)什么?是一個極簡的8位CPU核(如基于RISC-V或8051架構(gòu)),還是一個集成特定外設(shè)(如GPIO、定時器、ADC)的SoC(片上系統(tǒng))?定義清晰的功能、性能指標(biāo)(主頻、功耗)和接口需求。對于初學(xué)者,建議從實現(xiàn)一個經(jīng)典的開源處理器核(如PicoRV32)開始,而不是完全從零設(shè)計指令集。

第二階段:設(shè)計與仿真(在“云端”與本地構(gòu)建)

這是設(shè)計的核心環(huán)節(jié),主要在EDA軟件中完成。

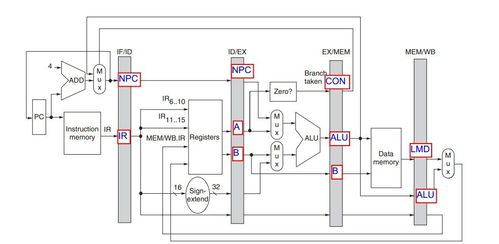

- 架構(gòu)設(shè)計與RTL編碼:根據(jù)你的目標(biāo),使用硬件描述語言編寫各個功能模塊(如ALU、寄存器堆、控制器、外設(shè))的代碼。這被稱為RTL(寄存器傳輸級)設(shè)計。

- 功能仿真:利用仿真工具(如Verilator、ModelSim)對你的RTL代碼進(jìn)行測試,驗證其邏輯功能是否正確。你需要編寫測試平臺(Testbench)來模擬各種輸入場景。

- 利用立創(chuàng)商城資源:在設(shè)計過程中,立創(chuàng)商城的價值開始凸顯:

- 元件選型參考:瀏覽商城上琳瑯滿目的現(xiàn)成單片機(如ST、GD、兆易等品牌),研究其數(shù)據(jù)手冊,可以為你自研芯片的外設(shè)設(shè)計(如UART、SPI、I2C接口)提供絕佳的參考標(biāo)準(zhǔn)和設(shè)計思路。

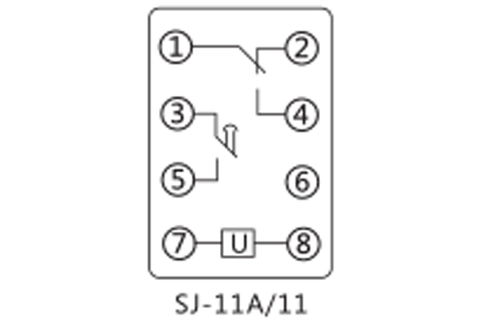

- 原理圖與封裝庫:立創(chuàng)EDA集成了強大的元件庫,其中包含大量標(biāo)準(zhǔn)元件的原理圖符號和PCB封裝。當(dāng)你設(shè)計自己的芯片時,其對外引腳(Package)的封裝定義可以參考這些標(biāo)準(zhǔn)封裝,為后續(xù)的PCB板級設(shè)計打下基礎(chǔ)。

第三階段:綜合、布局布線與驗證(走向“物理實現(xiàn)”)

將代碼轉(zhuǎn)化為實際的電路幾何圖形。這一步對個人而言最具挑戰(zhàn)性,但仍有路徑可循。

- 邏輯綜合:使用綜合工具(如Yosys,開源)將RTL代碼映射到目標(biāo)工藝庫的標(biāo)準(zhǔn)單元(如與非門、觸發(fā)器)。你需要一個工藝庫文件,這通常由芯片代工廠提供。對于學(xué)習(xí)和小批量,可以選擇FPGA作為實現(xiàn)載體,此時“工藝庫”就是FPGA廠商(如Xilinx、Altera)提供的庫。

- 布局布線:將綜合后的網(wǎng)表在芯片版圖上進(jìn)行物理排列和連線。這一步對工具和工藝依賴極強。個人項目可以:

- 使用開源工具鏈:如OpenROAD項目,旨在提供全流程的開源EDA工具,可實現(xiàn)從RTL到GDSII(版圖文件)的自動設(shè)計。

- 選擇MPW服務(wù):多項目晶圓服務(wù)允許你將設(shè)計與其他人的小設(shè)計共享一片晶圓,大幅降低制造成本。一些組織(如谷歌的SkyWater計劃,或國內(nèi)的公共服務(wù)平臺)會提供開源工藝庫和MPW流片機會。

- 后仿真與驗證:對生成版圖進(jìn)行時序、功耗等分析,確保滿足設(shè)計要求。

第四階段:制造、封裝與測試(借助生態(tài)實現(xiàn))

這是將設(shè)計變?yōu)閷嵨锏碾A段。

- 流片與封裝:通過MPW服務(wù)提交GDSII文件給晶圓廠制造裸片(Die)。之后,需要將裸片進(jìn)行封裝,變成我們常見的芯片外觀。這需要聯(lián)系專業(yè)的封裝測試廠。

- 立創(chuàng)商城的關(guān)鍵角色:

- PCB打樣與SMT貼片:這是立創(chuàng)商城最能直接助力的環(huán)節(jié)!你設(shè)計好的芯片最終需要焊接在PCB板上來驗證和運行。你可以使用立創(chuàng)EDA設(shè)計測試板(或最終產(chǎn)品板)的PCB,然后直接在立創(chuàng)商城享受快捷、低成本的PCB打樣和元器件采購、SMT貼片服務(wù),快速獲得可用于測試的實物電路板。

- 元器件配套:測試板上除了你的主控芯片,還需要電源、晶振、阻容、接口等外圍元件。這些都可以在立創(chuàng)商城一站式購齊,極大簡化了物料管理。

- 測試與調(diào)試:將封裝好的芯片焊接到測試板上,通過編程器/調(diào)試器(其元器件也可在立創(chuàng)商城采購)加載程序,進(jìn)行實際功能與性能測試。

第五階段:迭代與優(yōu)化

根據(jù)測試結(jié)果,返回設(shè)計階段進(jìn)行修改優(yōu)化。這是一個迭代的過程。

與建議

從零設(shè)計一個可用的單片機集成電路是一項系統(tǒng)工程,涉及“設(shè)計-驗證-制造-測試”全鏈條。對于個人或小團隊,可行路徑是:以開源處理器核和開源EDA工具為基礎(chǔ),以FPGA或MPW流片為實現(xiàn)手段,并以立創(chuàng)商城這樣的平臺作為強大的板級支持、物料供應(yīng)和快速原型制作的后盾。

行動路線圖建議:

1. 學(xué)習(xí)期:掌握數(shù)字電路、Verilog,在FPGA上實現(xiàn)一個開源CPU核(如RISC-V)。

2. 實踐期:為該CPU添加自定義外設(shè)(如通過APB總線掛載UART),并在FPGA上驗證。同時學(xué)習(xí)使用立創(chuàng)EDA設(shè)計一塊簡單的承載FPGA的測試板,并在立創(chuàng)商城完成打樣與焊接,體驗完整流程。

3. 探索期:研究開源EDA工具鏈(如Yosys+OpenROAD),嘗試將你的設(shè)計針對某一開源工藝庫進(jìn)行綜合與布局布線。關(guān)注國內(nèi)外MPW服務(wù)信息。

4. 實現(xiàn)期:若條件成熟,通過MPW服務(wù)流片,并再次利用立創(chuàng)商城制作精美的測試/應(yīng)用板,完成最終產(chǎn)品的集成與驗證。

這條路充滿挑戰(zhàn),但也正是硬件創(chuàng)新的魅力所在。立創(chuàng)商城作為連接設(shè)計與現(xiàn)實的橋梁,能讓你更專注于設(shè)計本身,而將繁瑣的物料、制板問題高效解決。祝你在這條硬核的創(chuàng)造之路上成功邁出第一步!

如若轉(zhuǎn)載,請注明出處:http://www.braccialini.com.cn/product/66.html

更新時間:2026-04-26 21:58:18