基于中、大規(guī)模集成電路的邏輯設(shè)計方法

隨著電子技術(shù)的飛速發(fā)展,中、大規(guī)模集成電路已成為現(xiàn)代邏輯設(shè)計的重要組成部分。本章將重點介紹如何利用這些集成電路進(jìn)行高效的邏輯設(shè)計,并探討其在實際應(yīng)用中的優(yōu)勢與挑戰(zhàn)。

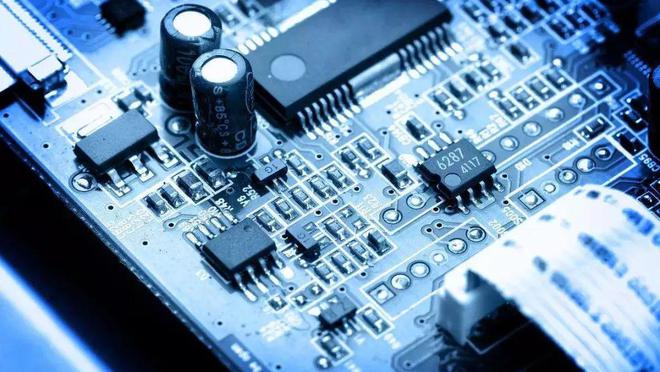

一、中、大規(guī)模集成電路概述

中、大規(guī)模集成電路(如CPLD、FPGA等)通過將成千上萬個邏輯門集成在單一芯片上,顯著提高了系統(tǒng)設(shè)計的密度和性能。與傳統(tǒng)的分立元件設(shè)計相比,它們具有更高的可靠性、更低的功耗以及更小的物理尺寸。例如,一片F(xiàn)PGA可以替代數(shù)百個標(biāo)準(zhǔn)邏輯芯片,從而簡化電路板布局并降低生產(chǎn)成本。

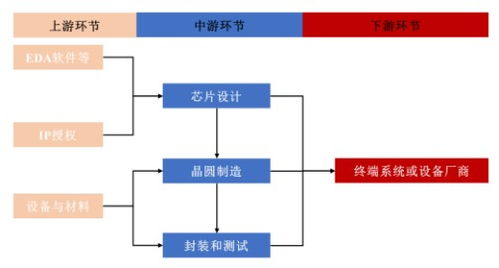

二、邏輯設(shè)計流程

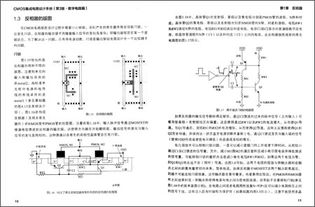

在設(shè)計基于中、大規(guī)模集成電路的系統(tǒng)時,通常采用自上而下的方法。設(shè)計者需要明確系統(tǒng)功能需求,并使用硬件描述語言(如VHDL或Verilog)進(jìn)行行為級建模。隨后,通過邏輯綜合工具將代碼轉(zhuǎn)換為門級網(wǎng)表,并利用布局布線工具在芯片上實現(xiàn)物理映射。仿真與驗證環(huán)節(jié)至關(guān)重要,以確保設(shè)計滿足時序和功能規(guī)范。生成比特流文件并下載到目標(biāo)器件中完成配置。

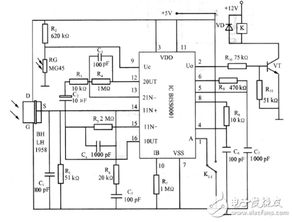

三、關(guān)鍵技術(shù)與工具

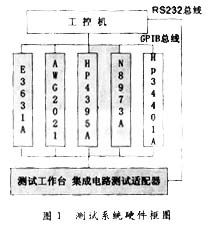

現(xiàn)代集成電路設(shè)計依賴于先進(jìn)的EDA(電子設(shè)計自動化)工具鏈。例如,Xilinx的Vivado和Intel的Quartus Prime提供了從設(shè)計輸入到硬件調(diào)試的完整解決方案。設(shè)計者需掌握時序分析、功耗優(yōu)化和故障診斷等技能,以應(yīng)對高速電路中的信號完整性問題。對于復(fù)雜系統(tǒng),還可采用IP核復(fù)用技術(shù),加速開發(fā)進(jìn)程并降低風(fēng)險。

四、應(yīng)用實例與趨勢

中、大規(guī)模集成電路已廣泛應(yīng)用于通信、汽車電子和人工智能等領(lǐng)域。以5G基站為例,F(xiàn)PGA被用于實現(xiàn)靈活的波束成形算法;在自動駕駛系統(tǒng)中,ASIC則專用于實時圖像處理。未來,隨著芯片制程的不斷進(jìn)步,三維集成和異構(gòu)計算將成為邏輯設(shè)計的新方向,進(jìn)一步推動電子系統(tǒng)的創(chuàng)新。

掌握中、大規(guī)模集成電路的設(shè)計方法對于現(xiàn)代工程師而言至關(guān)重要。通過合理選擇器件、優(yōu)化設(shè)計流程并利用先進(jìn)工具,我們能夠構(gòu)建出高性能、低成本的數(shù)字系統(tǒng),為科技進(jìn)步注入持續(xù)動力。

如若轉(zhuǎn)載,請注明出處:http://www.braccialini.com.cn/product/7.html

更新時間:2026-04-28 06:15:56