CMOS集成電路設計 從基礎到實踐

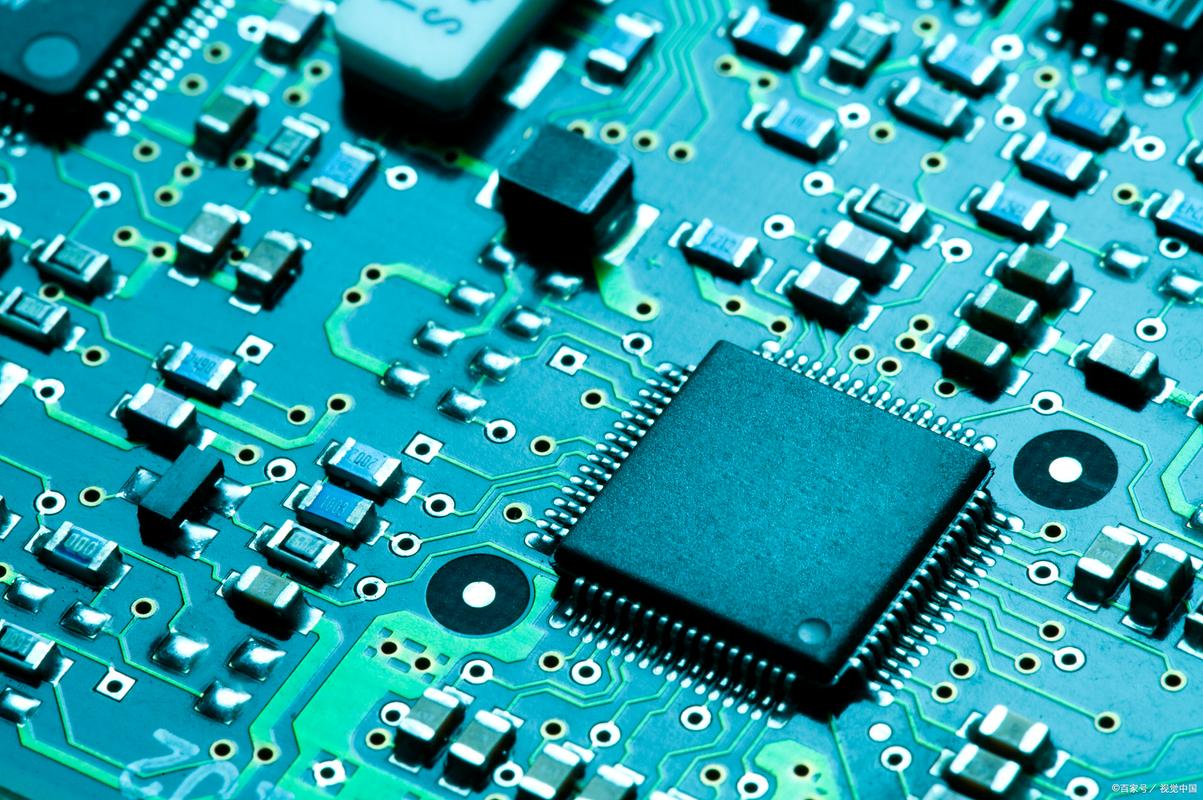

CMOS(互補金屬氧化物半導體)集成電路設計是現代電子工程的核心領域之一,廣泛應用于微處理器、存儲器、通信芯片和各類嵌入式系統。隨著半導體技術的不斷演進,CMOS設計已成為推動信息科技發展的關鍵驅動力。

一、CMOS集成電路設計基礎

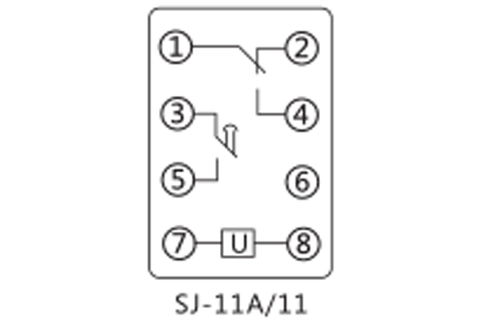

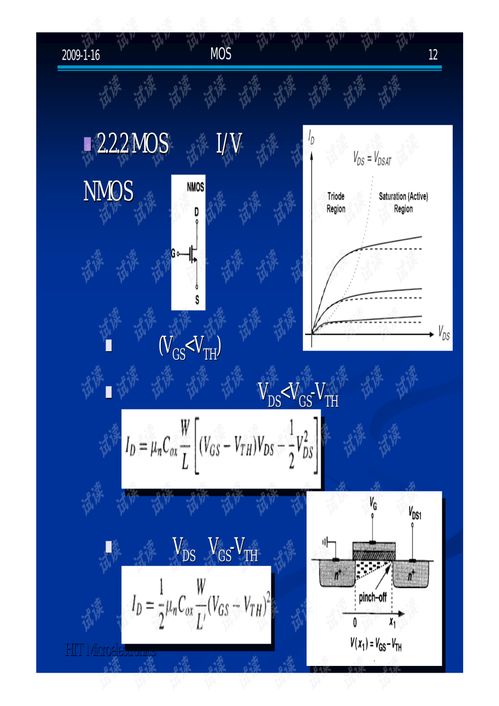

CMOS技術基于NMOS和PMOS晶體管的互補組合,具有低功耗、高噪聲容限和良好的集成度等優勢。設計流程通常包括系統規劃、電路設計、版圖實現、仿真驗證和制造測試等階段。其中,電路設計又可分為邏輯設計、模擬設計和混合信號設計三大類。

二、關鍵設計技術與挑戰

隨著工藝節點進入納米尺度,設計者面臨諸多挑戰:

- 功耗管理:靜態功耗和動態功耗的平衡成為關鍵,需采用多電壓域、時鐘門控等技術優化。

- 時序收斂:信號完整性、時鐘抖動和工藝變異要求更精確的時序分析。

- 可制造性設計:必須考慮光刻限制、化學機械拋光效應等制造約束。

- 可靠性設計:電遷移、熱載流子注入等老化機制需在設計中提前規避。

三、設計方法與工具鏈

現代CMOS設計依賴高度自動化的電子設計自動化工具:

- 前端設計:使用硬件描述語言進行RTL編碼,通過邏輯綜合生成門級網表。

- 后端設計:完成布局布線、時鐘樹合成和物理驗證,最終生成GDSII格式的版圖文件。

- 驗證流程:涵蓋功能仿真、形式驗證、靜態時序分析和物理驗證等多個維度。

四、未來發展趨勢

- 異構集成:通過3D-IC和芯粒技術整合不同工藝節點和功能的芯片模塊。

- AI輔助設計:機器學習算法正在加速設計空間探索和優化過程。

- 新興計算架構:存算一體、近似計算等創新架構為特定應用場景提供能效突破。

CMOS集成電路設計不僅需要深厚的半導體物理和電路理論功底,更要求設計者掌握跨學科的系統思維。隨著物聯網、人工智能和5G等新興技術的普及,CMOS設計將繼續在性能、功耗和成本之間尋求創新平衡,為數字社會奠定硬件基石。

如若轉載,請注明出處:http://www.braccialini.com.cn/product/81.html

更新時間:2026-04-28 15:01:22