CMOS模擬集成電路設計 從拉扎維課件到現代集成電路設計實踐

CMOS模擬集成電路設計是電子工程領域的核心課程之一,其重要性不言而喻。在這一領域中,Behzad Razavi(拉扎維)教授的經典教材和相關課件,已成為全球眾多高校和工程師學習與參考的基石。本文將探討拉扎維課件在CMOS模擬集成電路設計教學中的關鍵作用,并闡述其理論如何與現代集成電路設計實踐緊密結合。

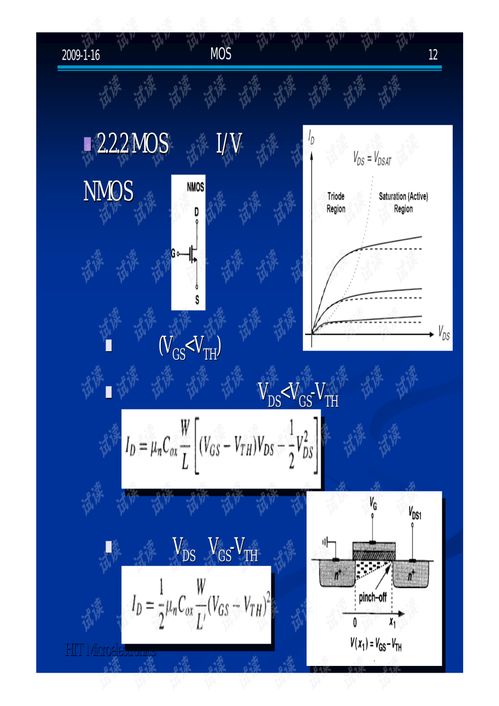

拉扎維教授的《模擬CMOS集成電路設計》一書及其配套課件,以其清晰的邏輯、深刻的洞察力和由淺入深的講解方式而著稱。課件內容通常涵蓋從MOSFET器件物理基礎、單級放大器、差分放大器、電流鏡、頻率響應、噪聲分析,到更復雜的模塊如運算放大器、穩定性與頻率補償、帶隙基準源、數據轉換器等核心主題。其最大特點在于,它不僅僅傳授電路拓撲和分析方法,更著重于培養設計直覺(Design Intuition)——即理解電路行為背后的物理本質和權衡(Trade-offs)。例如,在講解共源放大器時,會深入剖析增益、帶寬、功耗、噪聲和線性度之間的制約關系,這正是模擬設計的精髓所在。

課件與教材提供的更多是堅實的理論基礎和分析框架。要完成一個成功的集成電路設計,必須跨越理論到實踐的鴻溝。現代CMOS模擬集成電路設計實踐呈現出以下幾個鮮明特點:

工藝節點的不斷演進(從微米級到深亞微米乃至納米級)帶來了顯著的二階效應,如短溝道效應、遷移率退化、溝道長度調制以及日益嚴重的工藝偏差。拉扎維課件中基于長溝道模型的初步分析,在實際設計中必須通過先進的仿真工具(如SPICE)結合精確的工藝設計套件(PDK)進行驗證和優化。設計師需要深刻理解模型局限性,并學會在仿真中預見和解決實際問題。

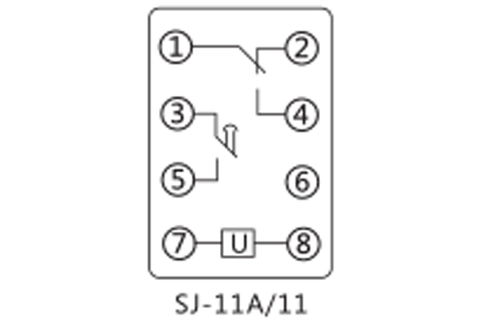

設計流程的高度自動化與系統化。現代設計遠不止于在晶體管級別手繪電路。它涉及系統規劃、架構選擇、電路設計、版圖實現、寄生參數提取、后仿真以及驗證等一系列復雜步驟。拉扎維課件中精美的電路圖需要轉化為符合設計規則(DRC)、電氣規則(ERC)和版圖與電路圖一致性(LVS)的物理版圖。版圖藝術本身——如匹配、對稱、降低寄生、防止閂鎖效應等——是課件理論的延伸和具體化,需要通過大量實踐來掌握。

模擬與數字的融合日益緊密。在當今主流的片上系統(SoC)中,模擬電路(如PLL、ADC/DAC、傳感器接口)往往深嵌于龐大的數字系統中。因此,模擬設計師必須考慮電源完整性、襯底噪聲耦合、數字開關噪聲的影響,并具備一定的混合信號設計觀念。這要求知識體系從純模擬向混合信號擴展。

設計指標的綜合優化與創新。面對物聯網、可穿戴設備、人工智能硬件等新興應用,對模擬電路提出了超高能效、超低功耗、高集成度等新要求。這驅動著設計師在拉扎維課件所授經典拓撲的基礎上,進行創新性的電路結構和設計技術探索,例如使用亞閾值區工作、時間域信號處理等。

拉扎維的課件為CMOS模擬集成電路設計提供了無與倫比的理論起點和思維訓練。它如同一張精準的地圖,指明了核心概念和主要路徑。但要真正到達目的地——設計出高性能、高可靠性的芯片,工程師必須在實際項目中,借助先進的EDA工具,深入理解工藝細節,掌握完整的設計流程,并不斷應對新的系統級挑戰。將拉扎維的經典理論與現代設計實踐相結合,持續學習與創新,是每一位模擬集成電路設計師成長的必由之路。

如若轉載,請注明出處:http://www.braccialini.com.cn/product/80.html

更新時間:2026-04-28 14:31:57